The industry is no longer far away from the next generation DDR6 memory standard for desktop and server platforms, and memory chip manufacturers are working with JEDEC to promote the formulation of relevant specifications. According to Korean media The Elec, major storage manufacturers such as SK Hynix, Samsung, and Micron have started DDR6 design in the laboratory and are gradually coordinating module development plans with substrate manufacturers. The above-mentioned collaborative research and development is carried out under the leadership of JEDEC, an industry standards organization, to ensure that the new generation of memory has a unified technical foundation at the design level.

It is reported that relevant manufacturers will have access to the first version of the DDR6 standard draft given by JEDEC as early as 2024, but key parameters such as voltage range, signal definition, power consumption packaging and pin layout have not yet been finalized. With the recent intensification of industry advancement, these gaps are expected to be gradually filled, and the standard finalization process will also be accelerated. Previously, several leading manufacturers have actually stepped out of the sample stage and entered a more stringent verification cycle, paving the way for subsequent mass production.

In terms of performance indicators that are of concern to the outside world, currently disclosed information shows that the target starting transmission rate of DDR6 is 8,800 MT/s, and plans to expand upward to 17,600 MT/s, which is almost equivalent to doubling the speed limit of the existing DDR5. The core of this substantial speed increase is that DDR6 adopts a 4×24-bit sub-channel architecture, which requires the introduction of new design ideas in terms of signal integrity. In contrast, the current DDR5 still uses a 2×32-bit sub-channel structure. The differences in channel division between the two generations of standards will put new requirements on controller design, wiring and PCB layer count.

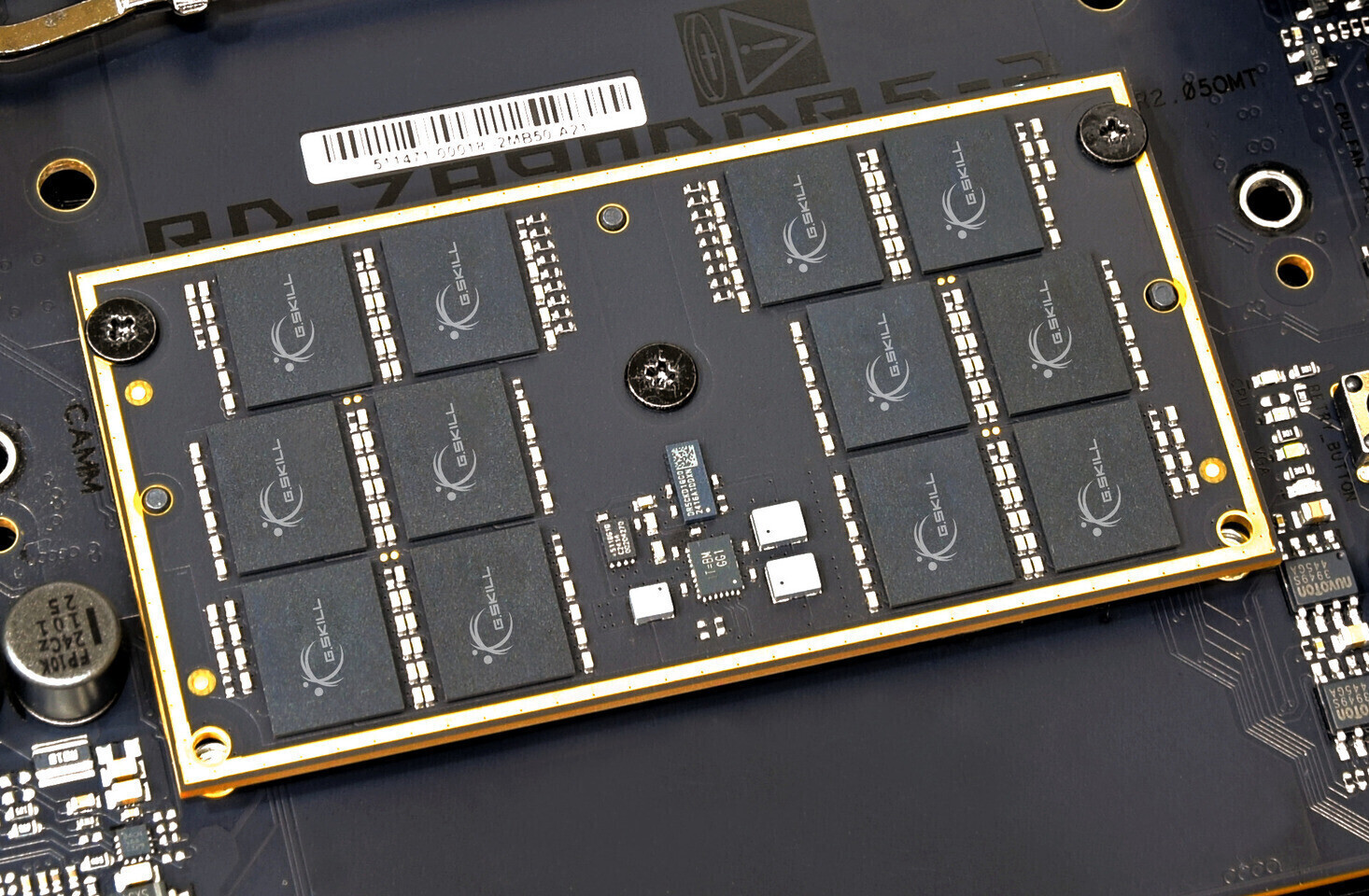

In the context of traditional DIMM modules encountering physical limits at high frequencies, the industry generally places its hopes on CAMM2 technology to alleviate the multiple bottlenecks of high-speed signals in space, wiring and interface forms. Current signs indicate that server platforms are expected to be the first to introduce DDR6, and then gradually move down to high-end notebook platforms after production capacity ramps up. Desktop consumer products may follow later.

Judging from the timetable, last year there was talk in the industry that DDR6 would be “launched” in 2027. However, the latest judgment is more inclined to regard 2027 as the key customer verification stage, and the real large-scale commercial use for the market is expected to be realized in 2028. At the same time, with the shipment of new generation servers and the overall application penetration rate of DDR5 reaching about 80% last year and expected to further climb to about 90% this year, DDR4’s role in the industry chain is gradually being regarded as a generation “to be exited”. This not only reserves more sufficient market space for the new standard, but also helps to release the production capacity of the wafer factory for the subsequent mass production of DDR6 chips and modules.